# **Section 6. Interrupts**

# HIGHLIGHTS

This section of the manual contains the following topics:

| 6.1 | Introduction                           |      |

|-----|----------------------------------------|------|

| 6.2 | Non-Maskable Traps                     |      |

| 6.3 | Interrupt Processing Timing            |      |

| 6.4 | Interrupt Control and Status Registers |      |

| 6.5 | Interrupt Setup Procedures             |      |

| 6.6 | Design Tips                            |      |

| 6.7 | Related Application Notes              |      |

| 6.8 | Revision History                       | 6-62 |

|     |                                        |      |

Interrupts

# 6.1 INTRODUCTION

The PIC24H Interrupt Controller module reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24H CPU. It has these features:

- Up to eight processor exceptions and software traps

- Seven user selectable priority levels

- Interrupt Vector Table (IVT) with up to 126 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debugging support

- Fixed interrupt entry and return latencies

### 6.1.1 Interrupt Vector Table

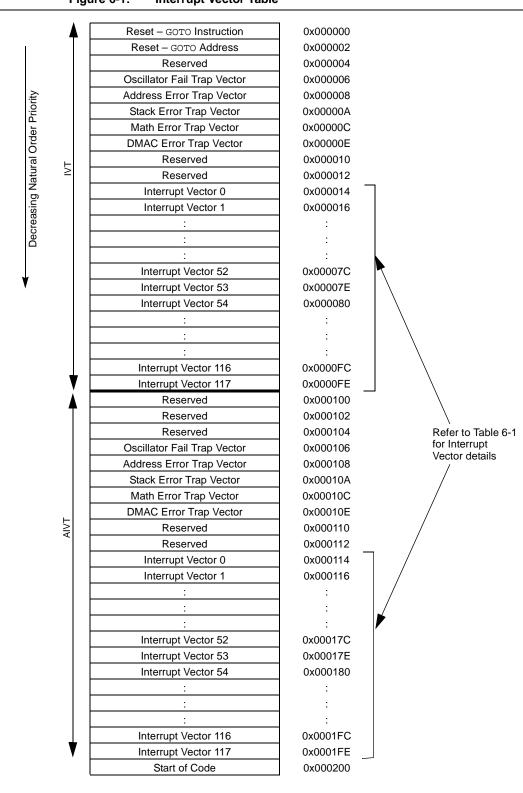

Figure 6-1 shows the IVT resides in program memory starting at location 0x000004. The IVT contains 126 vectors consisting of eight non-maskable trap vectors and up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

### 6.1.2 Alternate Vector Table

Figure 6-1 shows the AIVT that is located after the IVT. Access to the AIVT is provided by the Enable Alternate Interrupt Vector Table (ALTIVT) control bit in Interrupt Control Register 2 (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

### 6.1.3 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24H device clears its registers in response to a Reset, which forces the Program Counter (PC) to zero. The processor then begins program execution at location 0x000000. The user programs a GOTO instruction at the Reset address, that redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

6

Interrupts

| IRQ # | IVT Address | AIVT Address          | Interrupt Source                                    |

|-------|-------------|-----------------------|-----------------------------------------------------|

| 0     |             |                       | interrupt Source                                    |

| 0     |             | Highest Natural Order | Priority                                            |

|       | 0x000004    | 0x000104              | Reserved                                            |

| 1     | 0x000006    | 0x000106              | Oscillator Failure                                  |

| 2     | 0x000008    | 0x000108              | Address Error                                       |

| 3     | 0x00000A    | 0x00010A              | Stack Error                                         |

| 4     | 0x00000C    | 0x00010C              | Math Error                                          |

| 5     | 0x00000E    | 0x00010E              | DMAC Error                                          |

| 6     | 0x000010    | 0x000110              | Reserved                                            |

| 7     | 0x000012    | 0x000112              | Reserved                                            |

| 8     | 0x000014    | 0x000114              | INT0 – External Interrupt 0                         |

| 9     | 0x000016    | 0x000116              | IC1 – Input Compare 1                               |

| 10    | 0x000018    | 0x000118              | OC1 – Output Compare 1                              |

| 11    | 0x00001A    | 0x00011A              | T1 – Timer1                                         |

| 12    | 0x00001C    | 0x00011C              | DMA0 – DMA Channel 0                                |

| 13    | 0x00001E    | 0x00011E              | IC2 – Input Capture 2                               |

| 14    | 0x000020    | 0x000120              | OC2 – Output Compare 2                              |

| 15    | 0x000022    | 0x000122              | T2 – Timer2                                         |

| 16    | 0x000024    | 0x000124              | T3 – Timer3                                         |

| 17    | 0x000026    | 0x000126              | SPI1E – SPI 1 Fault                                 |

| 18    | 0x000028    | 0x000128              | SPI1 – SPI 1 Transfer Done                          |

| 19    | 0x00002A    | 0x00012A              | U1RX – UART1 Receiver                               |

| 20    | 0x00002C    | 0x00012C              | U1TX – UART1 Transmitter                            |

| 21    | 0x00002E    | 0x00012E              | AD1 – ADC1 Convert Done                             |

| 22    | 0x000030    | 0x000130              | DMA1 – DMA Channel 1                                |

| 23    | 0x000032    | 0x000132              | Reserved                                            |

| 24    | 0x000034    | 0x000134              | SI2C1 – I <sup>2</sup> C <sup>™</sup> 1 Slave Event |

| 25    | 0x000036    | 0x000136              | MI2C1 – I <sup>2</sup> C 1 Master Event             |

| 26    | 0x000038    | 0x000138              | Reserved                                            |

| 27    | 0x00003A    | 0x00013A              | CN – Input Change Interrupt                         |

| 28    | 0x00003C    | 0x00013C              | INT1 – External Interrupt 1                         |

| 29    | 0x00003E    | 0x00013E              | AD2 – ADC2 Convert Done                             |

| 30    | 0x000040    | 0x000140              | IC7 – Input Capture 7                               |

| 31    | 0x000042    | 0x000142              | IC8 – Input Capture 8                               |

| 32    | 0x000044    | 0x000144              | DMA2 – DMA Channel 2                                |

| 33    | 0x000046    | 0x000146              | OC3 – Output Compare 3                              |

| 34    | 0x000048    | 0x000148              | OC4 – Output Compare 4                              |

| 35    | 0x00004A    | 0x00014A              | T4 – Timer4                                         |

| 36    | 0x00004C    | 0x00014C              | T5 – Timer5                                         |

| 37    | 0x00004E    | 0x00014E              | INT2 – External Interrupt 2                         |

| 38    | 0x000050    | 0x000150              | U2RX – UART2 Receiver                               |

| 39    | 0x000052    | 0x000152              | U2TX – UART2 Transmitter                            |

| 40    | 0x000054    | 0x000154              | SPI2E – SPI2 Fault                                  |

| 41    | 0x000056    | 0x000156              | SPI2 – SPI2 Transfer Done                           |

| 42    | 0x000058    | 0x000158              | C1RX – CAN1 RX Data Ready                           |

| 43    | 0x00005A    | 0x00015A              | C1 – CAN1 Event                                     |

| 44    | 0x00005C    | 0x00015C              | DMA3 – DMA Channel 3                                |

| 45    | 0x00005E    | 0x00015E              | IC3 – Input Capture 3                               |

| 46    | 0x000060    | 0x000160              | IC4 – Input Capture 4                               |

| 47    | 0x000062    | 0x000162              | IC5 – Input Capture 5                               |

| 48    | 0x000064    | 0x000164              | IC6 – Input Capture 6                               |

| 49    | 0x000066    | 0x000166              | OC5 – Output Compare 5                              |

| 50    | 0x000068    | 0x000168              | OC6 – Output Compare 6                              |

| 51    | 0x00006A    | 0x00016A              | OC7 – Output Compare 7                              |

Table 6-1: Interrupt Vector Details

| IRQ #  | IVT Address       | AIVT Address           | Interrupt Source                                    |

|--------|-------------------|------------------------|-----------------------------------------------------|

| 52     | 0x00006C          | 0x00016C               | OC8 – Output Compare 8                              |

| 53     | 0x00006E          | 0x00016E               | Reserved                                            |

| 54     | 0x000070          | 0x000170               | DMA4 – DMA Channel 4                                |

| 55     | 0x000072          | 0x000172               | T6 – Timer6                                         |

| 56     | 0x000074          | 0x000174               | T7 – Timer7                                         |

| 57     | 0x000076          | 0x000176               | I2C2S – I <sup>2</sup> C <sup>™</sup> 2 Slave Event |

| 58     | 0x000078          | 0x000178               | I2C2M – I <sup>2</sup> C 2 Master Event             |

| 59     | 0x00007A          | 0x00017A               | T8 – Timer8                                         |

| 60     | 0x00007C          | 0x00017C               | T9 – Timer9                                         |

| 61     | 0x00007E          | 0x00017E               | INT3 – External Interrupt 3                         |

| 62     | 0x000080          | 0x000180               | INT4 – External Interrupt 4                         |

| 63     | 0x000082          | 0x000182               | C2RX – CAN2 RX Data Ready                           |

| 64     | 0x000084          | 0x000184               | C2 – CAN2 Event                                     |

| 65     | 0x000086          | 0x000186               | Reserved                                            |

| 66     | 0x000088          | 0x000188               | Reserved                                            |

| 67     | 0x00008A          | 0x00018A               | Reserved                                            |

| 68     | 0x00008C          | 0x00018C               | Reserved                                            |

| 69     | 0x00008E          | 0x00018E               | DMA5 – DMA Channel 5                                |

| 70     | 0x000090          | 0x000190               | Reserved                                            |

| 71     | 0x000092          | 0x000192               | Reserved                                            |

| 72     | 0x000094          | 0x000194               | Reserved                                            |

| 73     | 0x000096          | 0x000196               | U1E – UART1 Error Interrupt                         |

| 74     | 0x000098          | 0x000198               | U2E – UART2 Error Interrupt                         |

| 75     | 0x00009A          | 0x00019A               | Reserved                                            |

| 76     | 0x00009C          | 0x00019C               | DMA6 – DMA Channel 6                                |

| 77     | 0x00009E          | 0x00019E               | DMA7 – DMA Channel 7                                |

| 78     | 0x0000A0          | 0x0001A0               | C1TX – CAN1 TX Data Request                         |

| 79     | 0x0000A2          | 0x0001A2               | C2TX – CAN2 TX Data Request                         |

| 80     | 0x0000A4          | 0x0001A4               | Reserved                                            |

| 81     | 0x0000A6          | 0x0001A6               | Reserved                                            |

| 82     | 0x0000A8          | 0x0001A8               | Reserved                                            |

| 83-124 | 0x0000AA-0x0000FC | 0x0001AA-0x0001FC      | Reserved                                            |

| 125    | 0x0000FE          | 0x0001FE               | Reserved                                            |

|        |                   | Lowest Natural Order F | Priority                                            |

Table 6-1:

Interrupt Vector Details (Continued)

# 6.1.4 CPU Priority Status

The CPU can operate at one of 16 priority levels that range from 0-15. An interrupt or trap source must have a priority level greater than the current CPU priority to initiate an exception process. You can program peripheral and external interrupt sources for levels 0-7. CPU priority levels 8-15 are reserved for trap sources.

A trap is a non-maskable interrupt source intended to detect hardware and software problems (refer to **6.2** "**Non-Maskable Traps**"). The priority level for each trap source is fixed. Only one trap is assigned to a priority level. An interrupt source programmed to priority level 0 is effectively disabled, since it can never be greater than the CPU priority.

The current CPU priority level is indicated by the following status bits:

- CPU Interrupt Priority Level (IPL<2:0>) status bits in the CPU Status Register (SR<7:5>)

- CPU Interrupt Priority Level 3 (IPL3) status bit in the Core Control (CORCON<3>) register

The IPL<2:0> status bits are readable and writable, so the user application can modify these bits to disable all sources of interrupts below a given priority level. For example, if IPL<2:0> = 3, the CPU is not interrupted by any source with a programmed priority level of 0, 1, 2 or 3.

Trap events have higher priority than any user interrupt source. When the IPL3 bit is set, a trap event is in progress. The IPL3 bit can be cleared, but not set, by the user application. In some applications, you might need to clear the IPL3 bit when a trap has occurred and branch to an instruction other than the instruction after the one that originally caused the trap to occur.

All user interrupt sources can be disabled by setting IPL<2:0> = 111.

**Note:** The IPL<2:0> bits become read-only bits when interrupt nesting is disabled. For more information, refer to **6.2.4.2** "Interrupt Nesting".

# 6.1.5 Interrupt Priority

Each peripheral interrupt source can be assigned to one of seven priority levels. The user assignable interrupt priority control bits for each individual interrupt are located in the Least Significant 3 bits of each nibble within the IPCx registers. Bit 3 of each nibble is not used and is read as a '0'. These bits define the priority level assigned to a particular interrupt. The usable priority levels are 1 (lowest priority) through 7 (highest priority). If the IPC bits associated with an interrupt source are all cleared, the interrupt source is effectively disabled.

**Note:** The application program must disable the interrupts while reconfiguring the interrupt priority levels on the fly. Failure to disable interrupts can produce unexpected results,.

More than one interrupt request source can be assigned to a specific priority level. To resolve priority conflicts within a given user-assigned level, each source of interrupt has a natural order priority based on its location in the IVT. Table 6-1 shows the location of each interrupt source in the IVT. The lower numbered interrupt vectors have higher natural priority, while the higher numbered vectors have lower natural priority. The overall priority level for any pending source of interrupt is determined first by the user-assigned priority of that source in the IPCx register, then by the natural order priority within the IVT.

Natural order priority is used only to resolve conflicts between simultaneous pending interrupts with the same user assigned priority level. Once the priority conflict is resolved and the exception process begins, the CPU can be interrupted only by a source with higher user-assigned priority. Interrupts with the same user-assigned priority, but a higher natural order priority that become pending during the exception process, remain pending until the current exception process completes.

Assigning each interrupt source to one of seven priority levels enables the user application to give an interrupt with a low natural order priority a very high overall priority level. For example, the UART1 Rx Interrupt can be given a priority of 7, and the External Interrupt 0 (INT0) can be assigned to priority level 1, thus giving it a very low effective priority.

**Note:** The peripherals and sources of interrupt available in the IVT vary depending on the specific PIC24H device. The sources of interrupt shown in this document represent a comprehensive listing of all interrupt sources found on PIC24H devices. For further details, refer to the specific device data sheet.

# 6.2 NON-MASKABLE TRAPS

Traps are non-maskable, nestable interrupts that adhere to a fixed priority structure. Traps provide a means to correct erroneous operation during debugging and operation of the application. If the user application does not intend to correct a trap error condition, these vectors must be loaded with the address of a software routine to reset the device. Otherwise, the user application programs the trap vector with the address of a service routine that corrects the trap condition.

The PIC24H consists of the following implemented sources of non-maskable traps:

- Oscillator Failure Trap

- Stack Error Trap

- Address Error Trap

- Math Error Trap

- DMAC Error Trap

For many of the trap conditions, the instruction that caused the trap is allowed to complete before exception processing begins. Therefore, the user application may have to correct the action of the instruction that caused the trap.

Each trap source has a fixed priority as defined by its position in the IVT. An oscillator failure trap has the highest priority, while a DMA Controller (DMAC) error trap has the lowest priority (refer to Figure 6-1). In addition, trap sources are classified into two distinct categories: soft traps and hard traps.

# 6.2.1 Soft Traps

The DMAC error trap (priority level 10), math error trap (priority level 11), and stack error trap (priority level 12) are categorized as soft trap sources. Soft traps can be treated like non-maskable sources of interrupt that adhere to the priority assigned by their position in the IVT. Soft traps are processed like interrupts and require two cycles to be sampled and acknowledged prior to exception processing. Therefore, additional instructions may be executed before a soft trap is acknowledged.

### 6.2.1.1 STACK ERROR TRAP (SOFT TRAP, LEVEL 12)

The stack is initialized to 0x0800 during a Reset. A stack error trap is generated, if the Stack Pointer address is less than 0x0800.

A Stack Limit (SPLIM) register associated with the Stack Pointer is uninitialized at Reset. The stack overflow check is not enabled until a word is written to the SPLIM register.

All Effective Addresses (EA) generated using W15 as a source or destination pointer are compared against the value in the SPLIM register. If the EA is greater than the contents of the SPLIM register, a stack error trap generates. In addition, a stack error trap generates if the EA calculation wraps over the end of data space (0xFFFF).

A stack error can be detected in software by polling the Stack Error Trap (STKERR) status bit (INTCON1<2>). To avoid re-entering the Trap Service Routine, the STKERR status flag must be cleared (in software) before the program returns from the trap (with a RETFIE instruction).

### 6.2.1.2 MATH ERROR TRAP (SOFT TRAP, LEVEL 11)

A math error trap is generated by divide-by-zero events. Divide-by-zero traps cannot be disabled. The divide-by-zero check is performed during the first iteration of the REPEAT loop that executes the divide instruction. The Math Error Status (DIV0ERR) bit (INTCON1<6>) is set when this trap is detected.

A math error trap can be detected in software by polling the Math Error Status (MATHERR) bit (INTCON1<4>). To avoid re-entering the Trap Service Routine, the MATHERR status flag must be cleared (in software) before the program returns from the trap (with a RETFIE instruction). Before the MATHERR status bit can be cleared, all conditions that caused the trap to occur must also be cleared.

### 6.2.1.3 DMAC ERROR TRAP (SOFT TRAP, LEVEL 10)

A DMAC error trap occurs with these conditions:

- RAM write collision

- DMA-ready peripheral RAM write collision

Write collision errors are a serious enough threat to system integrity to warrant a non-maskable CPU trap event. If Both the CPU and a DMA channel attempt to write to a target address, the CPU is given priority and the DMA write is ignored. In this case, a DMAC error trap is generated and the DMAC Error Status (DMACERR) bit (INTCON1<5>) is set.

# 6.2.2 Hard Traps

Hard traps include exceptions of priority level 13 through level 15, inclusive. The address error (level 13) and oscillator error (level 14) traps fall into this category.

Like soft traps, hard traps are non-maskable sources of interrupt. The difference between hard traps and soft traps is that hard traps force the CPU to stop code execution after the instruction causing the trap to complete. Normal program execution flow does not resume until the trap is acknowledged and processed.

### 6.2.2.1 TRAP PRIORITY AND HARD TRAP CONFLICTS

If a higher priority trap occurs while any lower priority trap is in progress, processing of the lower-priority trap is suspended. The higher priority trap is acknowledged and processed. The lower priority trap remains pending until processing of the higher priority trap completes.

Each hard trap that occurs must be acknowledged before code execution of any type can continue. If a lower priority hard trap occurs while a higher priority trap is pending, acknowledged or is being processed, a hard-trap conflict occurs because the lower priority trap cannot be acknowledged until processing for the higher priority trap completes.

The device is automatically reset in a hard-trap conflict condition. The Trap Reset Flag (TRAPR) status bit in the Reset Control Register (RCON<15> in the Reset module) is set when the Reset occurs so that the condition can be detected in software.

### 6.2.2.2 OSCILLATOR FAILURE TRAP (HARD TRAP, LEVEL 14)

An oscillator failure trap event is generated for any of these reasons:

- The Fail-Safe Clock Monitor (FSCM) is enabled and has detected a loss of the system clock source

- · A loss of PLL lock has been detected during normal operation using the PLL

- The FSCM is enabled and the PLL fails to achieve lock at a Power-on Reset (POR)

An oscillator failure trap event can be detected in software by polling the Oscillator Failure Trap (OSCFAIL) status bit (INTCON1<1>) or the Clock Fail (CF) status bit (OSCCON<3> in the Oscillator module). To avoid re-entering the Trap Service Routine, the OSCFAIL status flag must be cleared (in software) before the program returns from the trap (with a RETFIE instruction).

For more information about the Fail-Safe Clock Monitor, refer to **Section 7** "**Oscillator**" (DS70227) and **Section 25** "**Device Configuration**" (DS70231). For the latest documentation, refer to the Microchip web site at www.microchip.com.

### 6.2.2.3 ADDRESS ERROR TRAP (HARD TRAP, LEVEL 13)

Operating conditions that can generate an address error trap include:

- A misaligned data word fetch is attempted. This condition occurs when an instruction performs a word access with the Least Significant bit (LSb) of the effective address set to '1'. The PIC24H CPU requires all word accesses to be aligned to an even address boundary

- A bit manipulation instruction uses the Indirect Addressing mode with the LSb of the effective address set to '1'

- A data fetch is attempted from unimplemented data address space

- Execution of a BRA #literal instruction or a GOTO #literal instruction, where literal is an unimplemented program memory address

• Execution of instructions after the Program Counter has been modified to point to unimplemented program memory addresses. The Program Counter can be modified by loading a value into the stack and executing a RETURN instruction

When an address error trap occurs, data space writes are inhibited so that data is not destroyed.

An address error can be detected in software by polling the ADDRERR status bit (INTCON1<3>). To avoid re-entering the Trap Service Routine, the ADDRERR status flag must be cleared (in software) before the program returns from the trap (with a RETFIE instruction).

### 6.2.3 Disable Interrupts Instruction

The DISI (disable interrupts) instruction can disable interrupts for up to 16384 instruction cycles. This instruction is useful for executing time-critical code segments.

The DISI instruction only disables interrupts with priority levels 1-6. Priority level 7 interrupts and all trap events can still interrupt the CPU when the DISI instruction is active.

The DISI instruction works in conjunction with the Disable Interrupts Count (DISICNT) register in the CPU. When the DISICNT register is non-zero, priority level 1-6 interrupts are disabled. The DISICNT register is decremented on each subsequent instruction cycle. When the DISICNT register counts down to zero, priority level 1-6 interrupts are re-enabled. The value specified in the DISI instruction includes all cycles due to PSV accesses, instruction stalls, etc.

The DISICNT register is both readable and writable. The user application can terminate the effect of a previous DISI instruction early by clearing the DISICNT register. The time that interrupts are disabled can also be increased by writing to, or adding to, the DISICNT register.

If the DISICNT register is zero, interrupts cannot be disabled by simply writing a non-zero value to the register. Interrupts must first be disabled by using the DISI instruction. Once the DISI instruction has executed and DISICNT holds a non-zero value, the application can extend the interrupt disable time by modifying the contents of DISICNT.

The DISI Instruction (DISI) status bit (INTCON2<14>) is set whenever interrupts are disabled as a result of the DISI instruction.

**Note:** The DISI instruction can be used to quickly disable all user interrupt sources if no source is assigned to CPU priority level 7.

### 6.2.4 Interrupt Operation

All interrupt event flags are sampled during each instruction cycle. A pending Interrupt Request (IRQ) is indicated by the flag bit = 1 in an IFSx register. The IRQ causes an interrupt if the corresponding bit in the Interrupt Enable (IECx) registers is set. For the rest of the instruction cycle in which the IRQ is sampled, the priorities of all pending interrupt requests are evaluated.

No instruction is aborted when the CPU responds to the IRQ. The instruction in progress when the IRQ is sampled is completed before the Interrupt Service Routine (ISR) is executed.

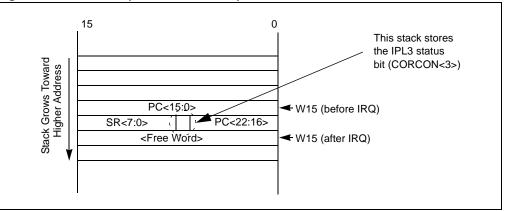

If the IPL<2:0> status bits (SR<7:5>) display a pending IRQ with a user-assigned priority level greater than the current processor level, an interrupt is presented to the processor. The processor then saves the following information on the software stack:

- Current PC value

- Low byte of the Processor Status register (SRL)

- IPL3 status bit (CORCON<3>)

These three values allow the return Program Counter address value, MCU status bits and the current processor priority level to automatically save.

After this information saves on the stack, the CPU writes the priority level of the pending interrupt into the IPL<2:0> bit locations. This action disables all interrupts of lower or equal priority until the ISR is terminated using the RETFIE instruction.

### 6.2.4.1 RETURN FROM INTERRUPT

The RETFIE (Return from Interrupt) instruction unstacks the PC return address, IPL3 status bit and SRL register to return the processor to the state and priority level that existed before the interrupt sequence.

### 6.2.4.2 INTERRUPT NESTING

Interrupts are nestable by default. Any ISR in progress can be interrupted by another source of interrupt with a higher user-assigned priority level. Interrupt nesting can be disabled by setting the Interrupt Nesting Disable (NSTDIS) control bit (INTCON1<15>). When the NSTDIS control bit is set, all interrupts in progress force the CPU priority to level 7 by setting IPL<2:0> = 111. This action effectively masks all other sources of interrupt until a RETFIE instruction executes. When interrupt nesting is disabled, the user-assigned interrupt priority levels have no effect except to resolve conflicts between simultaneous pending interrupts.

The IPL<2:0> bits (SR<7:5>) become read-only when interrupt nesting is disabled. This prevents the user software from setting IPL<2:0> to a lower value, which would effectively re-enable interrupt nesting.

### 6.2.5 Wake-Up from Sleep and Idle

Any source of interrupt that is individually enabled, using its corresponding control bit in the IECx registers, can wake-up the processor from Sleep or Idle mode. When the interrupt status flag for a source is set and the interrupt source is enabled by the corresponding bit in the IEC Control registers, a wake-up signal is sent to the PIC24H CPU. When the device wakes from Sleep or Idle mode, one of two actions occur:

- If the interrupt priority level for that source is greater than the current CPU priority level, the processor processes the interrupt and branches to the ISR for the interrupt source

- If the user-assigned interrupt priority level for the source is lower than, or equal to, the current CPU priority level, the processor continues execution, starting with the instruction immediately following the PWRSAV instruction that previously put the CPU in Sleep or Idle mode

**Note:** User interrupt sources assigned to CPU priority level 0 cannot wake the CPU from Sleep or Idle mode, because the interrupt source is effectively disabled. To use an interrupt as a wake-up source, the program must assign the CPU priority level for the interrupt to level 1 or greater.

# 6.2.6 Analog-to-Digital Converter (ADC) External Conversion Request

The INT0 external interrupt request pin is shared with the ADC as an external conversion request signal. The INT0 interrupt source has programmable edge polarity, which is also available to the ADC external conversion request feature.

# 6.2.7 External Interrupt Support

The PIC24H supports up to five external interrupt pin sources (INT0-INT4). Each external interrupt pin has edge detection circuitry to detect the interrupt event. The INTCON2 register has five control bits (INT0EP-INT4EP) that select the polarity of the edge detection circuitry. Each external interrupt pin can be programmed to interrupt the CPU on a rising edge or falling edge event. For further details, refer to Register 6-4.

# 6.3 INTERRUPT PROCESSING TIMING

# 6.3.1 Interrupt Latency for One-Cycle Instructions

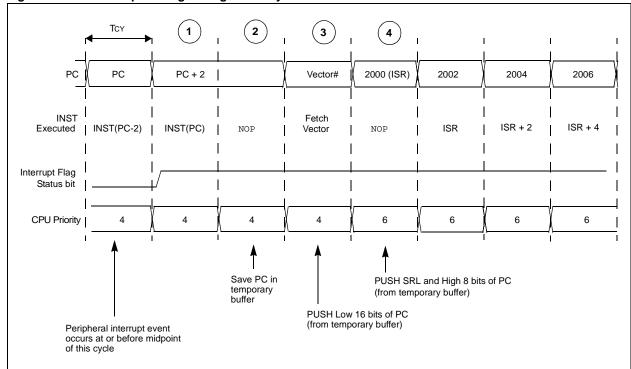

Figure 6-3 shows the sequence of events when a peripheral interrupt is asserted during a one-cycle instruction. The interrupt process takes four instruction cycles. Each cycle in the figure is numbered for reference.

The interrupt flag status bit is set during the instruction cycle after the peripheral interrupt occurs. The current instruction completes during this instruction cycle. In the second instruction cycle after the interrupt event, the contents of the PC and Lower Byte Status (SRL) registers are saved into a temporary buffer register. The second cycle of the interrupt process is executed as a NOP to maintain consistency with the sequence taken during a two-cycle instruction (refer to **6.3.2 "Interrupt Latency for Two-Cycle Instructions"**). In the third cycle, the PC is loaded with the vector table address for the interrupt source and the starting address of the ISR is fetched. In the fourth cycle, the PC is loaded with the ISR address. The fourth cycle is executed as a NOP, while the first instruction in the ISR is fetched.

#### Figure 6-3: Interrupt Timing During a One-Cycle Instruction

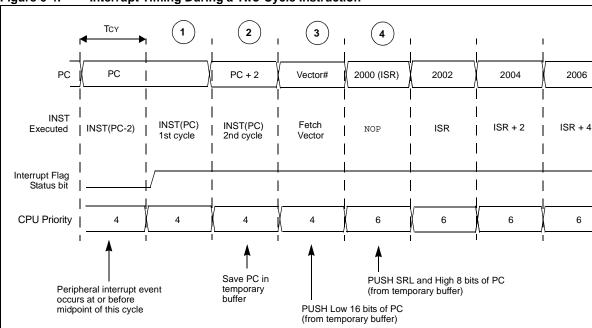

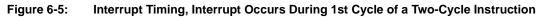

# 6.3.2 Interrupt Latency for Two-Cycle Instructions

The interrupt latency during a two-cycle instruction is the same as during a one-cycle instruction. The first and second cycle of the interrupt process allow the two-cycle instruction to complete execution. The timing diagram in Figure 6-4 shows the peripheral interrupt event occurring in the instruction cycle prior to execution of the two-cycle instruction.

Figure 6-5 shows the timing when a peripheral interrupt coincides with the first cycle of a two-cycle instruction. In this case, the interrupt process completes as if for a one-cycle instruction (refer to 6.3.1 "Interrupt Latency for One-Cycle Instructions").

Figure 6-4: Interrupt Timing During a Two-Cycle Instruction

# 6.3.3 Returning from Interrupt

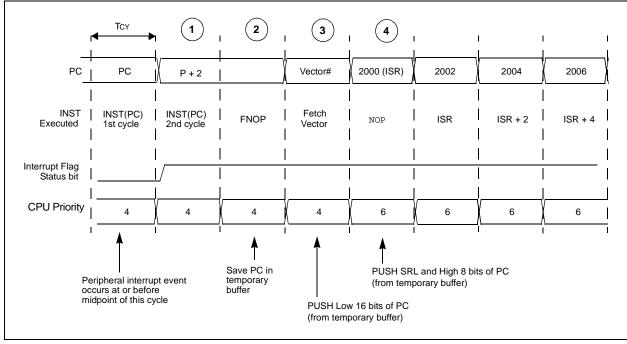

To return from an interrupt, the program must call the RETFIE instruction. During the first two cycles of a RETFIE instruction, the contents of the PC and the SRL register are popped from the stack. The third instruction cycle fetches the instruction addressed by the updated program counter. This cycle executes as a NOP instruction. On the fourth cycle, program execution resumes at the point where the interrupt occurred.

Figure 6-6: Return from Interrupt Timing

# 6.3.4 Special Conditions for Interrupt Latency

The PIC24H allows the current instruction to complete when a peripheral interrupt source becomes pending. The interrupt latency is the same for both one- and two-cycle instructions. However, certain conditions can increase interrupt latency by one cycle, depending on when the interrupt occurs. If a fixed latency is critical to the application, you should avoid these conditions:

- Executing a MOV.D instruction that uses PSV to access a value in program memory space

- · Appending an instruction stall cycle to any two-cycle instruction

- Appending an instruction stall cycle to any one-cycle instruction that performs a PSV access

- A bit test and skip instruction (BTSC, BTSS) that uses PSV to access a value in the program memory space

# 6.4 INTERRUPT CONTROL AND STATUS REGISTERS

These are associated with the interrupt controller:

### • INTCON1, INTCON2 Registers

- The following registers control global interrupt functions:

- INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources.

- INTCON2 controls external interrupt request signal behavior and use of the alternate vector table.

- IFSx: Interrupt Flag Status Registers

All interrupt request flags are maintained in the IFSx registers, where 'x' denotes the register number. Each source of interrupt has a status bit, set by the respective peripherals or external signal and cleared by software.

- IECx: Interrupt Enable Control Registers All Interrupt Enable Control bits are maintained in the IECx registers, where 'x' denotes the register number. These control bits are used to individually enable interrupts from the peripherals or external signals.

- IPCx: Interrupt Priority Control Registers

Each user interrupt source can be assigned to one of eight priority levels. The IPC registers set the interrupt priority level for each source of interrupt.

SR: CPU Status Register

The SR is not specifically part of the interrupt controller hardware, but it contains the IPL<2:0> status bits (SR<7:5>) that indicate the current CPU priority level. The user application can change the current CPU priority level by writing to the IPL bits.

CORCON: Core Control Register

The CORCON register is not specifically part of the interrupt controller hardware, but it contains the IPL3 status bit, which indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

Each register is described in detail in the following sections.

**Note:** The total number and type of interrupt sources depend on the device variant. For further details, refer to the specific device data sheet.

# 6.4.1 Assignment of Interrupts to Control Registers

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 6-1. For example, the INT0 (External Interrupt 0) source has vector number and natural order priority 0. Thus, the External Interrupt 0 Flag Status (INT0IF) bit is found in IFS0<0>. The INT0 interrupt uses bit 0 of the IEC0 register as its Enable bit. The IPC0<2:0> bits assign the interrupt priority level for the INT0 interrupt.

| U-0                                                                                                                    | U-0                                          | U-0              | U-0                                       | U-0                        | U-0                  | U-0   | U-0                |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------|-------------------------------------------|----------------------------|----------------------|-------|--------------------|--|--|--|

| —                                                                                                                      | —                                            | —                | —                                         | —                          | —                    | —     | —                  |  |  |  |

| bit 15                                                                                                                 |                                              |                  |                                           |                            |                      |       | bit 8              |  |  |  |

|                                                                                                                        |                                              |                  |                                           |                            |                      |       |                    |  |  |  |

| R/W-0                                                                                                                  | R/W-0                                        | R/W-0            | R-0                                       | R/W-0                      | R/W-0                | R/W-0 | R/W-0              |  |  |  |

|                                                                                                                        | IPL<2:0>                                     |                  | RA                                        | N                          | OV                   | Z     | С                  |  |  |  |

| bit 7                                                                                                                  |                                              |                  |                                           |                            |                      |       | bit 0              |  |  |  |

|                                                                                                                        |                                              |                  |                                           |                            |                      |       |                    |  |  |  |

| Legend:                                                                                                                |                                              |                  |                                           |                            |                      |       |                    |  |  |  |

| R = Readable                                                                                                           | e bit                                        | W = Writable     | le bit U = Unimplemented bit, read as '0' |                            |                      |       |                    |  |  |  |

| -n = Value at                                                                                                          | POR                                          | '1' = Bit is set | 1' = Bit is set                           |                            | '0' = Bit is cleared |       | x = Bit is unknown |  |  |  |

|                                                                                                                        |                                              |                  |                                           |                            |                      |       |                    |  |  |  |

| bit 15-8                                                                                                               | Unimpleme                                    | nted: Read as    | '0'                                       |                            |                      |       |                    |  |  |  |

| bit 7-5                                                                                                                | IPL<2:0>: C                                  | PU Interrupt Pr  | ioritv Level Sta                          | itus bits <sup>(1,2)</sup> |                      |       |                    |  |  |  |

|                                                                                                                        |                                              | •                | •                                         |                            | ts disabled          |       |                    |  |  |  |

| 111 = CPU interrupt priority level is 7 (15). User interrupts disabled<br>110 = CPU interrupt priority level is 6 (14) |                                              |                  |                                           |                            |                      |       |                    |  |  |  |

|                                                                                                                        |                                              |                  |                                           |                            |                      |       |                    |  |  |  |

|                                                                                                                        | 101 = CPU interrupt priority level is 5 (13) |                  |                                           |                            |                      |       |                    |  |  |  |

|                                                                                                                        | 100 = CPU interrupt priority level is 4 (12) |                  |                                           |                            |                      |       |                    |  |  |  |

|                                                                                                                        | 011 = CPU interrupt priority level is 3 (11) |                  |                                           |                            |                      |       |                    |  |  |  |

|                                                                                                                        | 010 = CPU interrupt priority level is 2 (10) |                  |                                           |                            |                      |       |                    |  |  |  |

### Register 6-1: SR: Status Register (In CPU)

| Noto 1: | The IDL $220$ bits are consistentiated with the IDL $22$ bit (COPCON-22) to form the CDL interrupt priority |

|---------|-------------------------------------------------------------------------------------------------------------|

(Refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157) for description of SR bits.)

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU interrupt priority level. The value in parentheses indicates the IPL if IPL<3> = 1.

- 2: The IPL<2:0> status bits are read only when NSTDIS = 1 (INTCON1<15>).

001 = CPU interrupt priority level is 1 (9) 000 = CPU interrupt priority level is 0 (8)

Not used by the Interrupt Controller

bit 4-0

| U-0           | U-0                                                                                                    | U-0              | U-0                    | U-0                                | U-0   | U-0                | U-0   |  |  |

|---------------|--------------------------------------------------------------------------------------------------------|------------------|------------------------|------------------------------------|-------|--------------------|-------|--|--|

| —             | —                                                                                                      | —                | —                      | —                                  | —     | —                  | —     |  |  |

| bit 15        |                                                                                                        |                  |                        |                                    |       |                    | bit 8 |  |  |

|               |                                                                                                        |                  |                        |                                    |       |                    |       |  |  |

| U-0           | U-0                                                                                                    | U-0              | U-0                    | R/C-0                              | R/W-0 | U-0                | U-0   |  |  |

| —             | —                                                                                                      | —                | —                      | IPL3                               | PSV   | —                  | _     |  |  |

| bit 7         |                                                                                                        | •                | •                      |                                    |       |                    | bit 0 |  |  |

|               |                                                                                                        |                  |                        |                                    |       |                    |       |  |  |

| Legend:       |                                                                                                        |                  |                        |                                    |       |                    |       |  |  |

| R = Readable  | e bit                                                                                                  | W = Writable     | bit                    | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value at | POR                                                                                                    | '1' = Bit is set | t '0' = Bit is cleared |                                    | eared | x = Bit is unknown |       |  |  |

|               |                                                                                                        |                  |                        |                                    |       |                    |       |  |  |

| bit 15-4      | Unimplemen                                                                                             | ted: Read as     | ʻ0'                    |                                    |       |                    |       |  |  |

| bit 3         | IPL3: CPU In                                                                                           | terrupt Priority | Level Status b         | oit 3(1)                           |       |                    |       |  |  |

|               |                                                                                                        |                  | vel is greater th      |                                    |       |                    |       |  |  |

|               |                                                                                                        |                  | vel is 7 or less       |                                    |       |                    |       |  |  |

| bit 2         | Not used by                                                                                            | the Interrupt    | Controller             |                                    |       |                    |       |  |  |

|               | (Refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157), for description of CORCON bits.) |                  |                        |                                    |       |                    |       |  |  |

|               |                                                                                                        |                  |                        |                                    |       |                    |       |  |  |

| Register 6-2: | CORCON: Core Control Register |

|---------------|-------------------------------|

|---------------|-------------------------------|

Unimplemented: Read as '0'

Note 1: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

© 2008 Microchip Technology Inc.

bit 1-0

| R/W-0              | U-0                                                                                                                                     | U-0                                                                     | U-0             | U-0              | U-0              | U-0             | U-0   |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|-------|

| NSTDIS             |                                                                                                                                         | —                                                                       | —               | —                | —                | —               | _     |

| bit 15             |                                                                                                                                         |                                                                         |                 |                  |                  |                 | bit 8 |

|                    |                                                                                                                                         |                                                                         |                 |                  |                  |                 |       |

| U-0                | R/W-0                                                                                                                                   | R/W-0                                                                   | R/W-0           | R/W-0            | R/W-0            | R/W-0           | U-0   |

|                    | DIV0ERR                                                                                                                                 | DMACERR                                                                 | MATHERR         | ADDRERR          | STKERR           | OSCFAIL         | —     |

| bit 7              |                                                                                                                                         |                                                                         |                 |                  |                  |                 | bit 0 |

| Legend:            |                                                                                                                                         |                                                                         |                 |                  |                  |                 |       |

| R = Readable       | bit                                                                                                                                     | W = Writable                                                            | bit             | U = Unimplei     | mented bit, read | as '0'          |       |

| -n = Value at F    | POR                                                                                                                                     | '1' = Bit is set                                                        |                 | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

| bit 15<br>bit 14-7 | 1 = Interrupt<br>0 = Interrupt                                                                                                          | errupt Nesting I<br>nesting is disa<br>nesting is enat<br>nted: Read as | bled<br>bled    |                  |                  |                 |       |

| bit 6              | <b>DIV0ERR:</b> Di<br>1 = Divide-by                                                                                                     | ivide-by-zero E<br>-zero error tra<br>-zero error tra                   | rror Status bit |                  | zero             |                 |       |

| bit 5              | 1 = DMAC tra                                                                                                                            | DMAC Error S<br>ap has occurre<br>ap has not occ                        | d               |                  |                  |                 |       |

| bit 4              | 1 = Math erro                                                                                                                           | Math Error Stat<br>or trap has occ<br>or trap has not                   | urred           |                  |                  |                 |       |

| bit 3              | 1 = Address                                                                                                                             | Address Error<br>error trap has o<br>error trap has i                   | occurred        |                  |                  |                 |       |

| bit 2              | <b>STKERR:</b> Stack Error Trap Status bit<br>1 = Stack error trap has occurred<br>0 = Stack error trap has not occurred                |                                                                         |                 |                  |                  |                 |       |

| bit 1              | OSCFAIL: Oscillator Failure Trap Status bit<br>1 = Oscillator failure trap has occurred<br>0 = Oscillator failure trap has not occurred |                                                                         |                 |                  |                  |                 |       |

| bit 0              | Unimplemen                                                                                                                              | ted: Read as                                                            | ʻ0'             |                  |                  |                 |       |

|                    |                                                                                                                                         |                                                                         |                 |                  |                  |                 |       |

| R/W-0           | R-0                                                                                                                                     | U-0                                                | U-0    | U-0              | U-0              | U-0             | U-0    |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------|------------------|------------------|-----------------|--------|

| ALTIVT          | DISI                                                                                                                                    | —                                                  |        |                  |                  |                 |        |

| bit 15          |                                                                                                                                         |                                                    |        |                  |                  |                 | bit 8  |

| U-0             | U-0                                                                                                                                     | U-0                                                | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| 0-0             | 0-0                                                                                                                                     | 0-0                                                | INT4EP | INT3EP           | INT2EP           | INT1EP          | INT0EP |

| bit 7           |                                                                                                                                         |                                                    |        | INTSEF           | INTZEF           |                 | bit C  |

|                 |                                                                                                                                         |                                                    |        |                  |                  |                 |        |

| Legend:         |                                                                                                                                         |                                                    |        |                  |                  |                 |        |

| R = Readable I  |                                                                                                                                         | W = Writable                                       |        | •                | nented bit, read |                 |        |

| -n = Value at P | OR                                                                                                                                      | '1' = Bit is se                                    | et     | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 14          | DISI: DISI In                                                                                                                           | truction is acti                                   | us bit |                  |                  |                 |        |

| bit 13-5        | Unimplemen                                                                                                                              | ted: Read as                                       | ʻ0'    |                  |                  |                 |        |

| bit 4           | 1 = Interrupt of                                                                                                                        |                                                    | dge    | Polarity Select  | t bit            |                 |        |

| bit 3           | 1 = Interrupt of                                                                                                                        | ernal Interrupt<br>on negative e<br>on positive ed | dge    | Polarity Select  | t bit            |                 |        |

| bit 2           | <b>INT2EP:</b> External Interrupt 2 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge<br>0 = Interrupt on positive edge |                                                    |        |                  |                  |                 |        |

| bit 1           | <b>INT1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge<br>0 = Interrupt on positive edge |                                                    |        |                  |                  |                 |        |

| bit 0           | <b>INTOEP:</b> Extended 1 = Interrupt of                                                                                                |                                                    |        | Polarity Select  | t bit            |                 |        |

Register 6-4: INTCON2: Interrupt Control Register 2

Interrupts

| Register 6-5:   | IFS0: Interr                                                                                           | rupt Flag Stati                  | us Register U    |                  |                  |                 |        |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------|----------------------------------|------------------|------------------|------------------|-----------------|--------|--|--|--|--|

| U-0             | R/W-0                                                                                                  | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| —               | DMA1IF                                                                                                 | AD1IF                            | U1TXIF           | U1RXIF           | SPI1IF           | SPI1EIF         | T3IF   |  |  |  |  |

| bit 15          |                                                                                                        |                                  |                  | •                |                  |                 | bit 8  |  |  |  |  |

| R/W-0           | R/W-0                                                                                                  | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| T2IF            | OC2IF                                                                                                  | IC2IF                            | DMA01IF          | T1IF             | OC1IF            | IC1IF           | INTOIF |  |  |  |  |

| bit 7           | 00211                                                                                                  | 10211                            | Billi Korri      |                  | 00111            |                 | bit (  |  |  |  |  |

| Legend:         |                                                                                                        |                                  |                  |                  |                  |                 |        |  |  |  |  |

| R = Readable    | bit                                                                                                    | W = Writable                     | bit              | U = Unimplei     | mented bit, rea  | d as '0'        |        |  |  |  |  |

| -n = Value at I | POR                                                                                                    | '1' = Bit is se                  | t                | '0' = Bit is cle | eared            | x = Bit is unkr | nown   |  |  |  |  |

| bit 15          | Unimplemen                                                                                             | ted: Read as                     | 'O'              |                  |                  |                 |        |  |  |  |  |

| bit 14          | DMA1IF: DM                                                                                             | A Channel 1 E                    | ata Transfer C   | complete Interr  | rupt Flag Status | s bit           |        |  |  |  |  |

|                 | 1 = Interrupt                                                                                          | request has oc<br>request has no | curred           | ·                |                  |                 |        |  |  |  |  |

| bit 13          | •                                                                                                      | •                                |                  | upt Flag Statu   | ıs bit           |                 |        |  |  |  |  |

|                 | AD1IF: ADC1 Conversion Complete Interrupt Flag Status bit<br>1 = Interrupt request has occurred        |                                  |                  |                  |                  |                 |        |  |  |  |  |

|                 | 0 = Interrupt request has not occurred                                                                 |                                  |                  |                  |                  |                 |        |  |  |  |  |

| bit 12          | U1TXIF: UART1 Transmitter Interrupt Flag Status bit                                                    |                                  |                  |                  |                  |                 |        |  |  |  |  |

|                 |                                                                                                        | request has oc<br>request has no |                  |                  |                  |                 |        |  |  |  |  |

| bit 11          | U1RXIF: UART1 Receiver Interrupt Flag Status bit                                                       |                                  |                  |                  |                  |                 |        |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                  |                  |                  |                  |                 |        |  |  |  |  |

| bit 10          | SPI1IF: SPI1 Event Interrupt Flag Status bit                                                           |                                  |                  |                  |                  |                 |        |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                  |                  |                  |                  |                 |        |  |  |  |  |

| bit 9           | SPI1EIF: SPI1 Fault Interrupt Flag Status bit                                                          |                                  |                  |                  |                  |                 |        |  |  |  |  |

|                 |                                                                                                        | request has oc<br>request has no |                  |                  |                  |                 |        |  |  |  |  |

| bit 8           | T3IF: Timer3 Interrupt Flag Status bit                                                                 |                                  |                  |                  |                  |                 |        |  |  |  |  |

|                 | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                           |                                  |                  |                  |                  |                 |        |  |  |  |  |

| bit 7           | <b>T2IF:</b> Timer2 Interrupt Flag Status bit                                                          |                                  |                  |                  |                  |                 |        |  |  |  |  |

|                 | 1 = Interrupt request has occurred                                                                     |                                  |                  |                  |                  |                 |        |  |  |  |  |

|                 | 0 = Interrupt request has not occurred                                                                 |                                  |                  |                  |                  |                 |        |  |  |  |  |

| bit 6           | -                                                                                                      | -                                | nannel 2 Interru | upt Flag Status  | s bit            |                 |        |  |  |  |  |

|                 | •                                                                                                      | request has oc<br>request has no |                  |                  |                  |                 |        |  |  |  |  |

| bit 5           | IC2IF: Input (                                                                                         | Capture Chanr                    | el 2 Interrupt F | lag Status bit   |                  |                 |        |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                  |                  |                  |                  |                 |        |  |  |  |  |

| bit 4           | DMA0IF: DM                                                                                             | A Channel 0 E                    | ata Transfer C   | omplete Interi   | rupt Flag Status | s bit           |        |  |  |  |  |

|                 | •                                                                                                      | request has or                   |                  |                  |                  |                 |        |  |  |  |  |

|                 | -                                                                                                      | request has no                   |                  |                  |                  |                 |        |  |  |  |  |

| bit 3           |                                                                                                        | Interrupt Flag                   |                  |                  |                  |                 |        |  |  |  |  |

|                 |                                                                                                        | request has oc<br>request has no |                  |                  |                  |                 |        |  |  |  |  |

|                 |                                                                                                        |                                  |                  |                  |                  |                 |        |  |  |  |  |

# Register 6-5: IFS0: Interrupt Flag Status Register 0

# Register 6-5: IFS0: Interrupt Flag Status Register 0 (Continued)

1 = Interrupt request has occurred0 = Interrupt request has not occurred

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit  |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit              |

6 Interrupts

| ivegister 0-0.  | ii or. iiiteri                                                                                                               | upt i lag Statu                         | is neglater i   |                  |                 |                 |         |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|------------------|-----------------|-----------------|---------|--|--|--|--|

| R/W-0           | R/W-0                                                                                                                        | R/W-0                                   | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

| U2TXIF          | U2RXIF                                                                                                                       | INT2IF                                  | T5IF            | T4IF             | OC4IF           | OC3IF           | DMA2IF  |  |  |  |  |

| bit 15          |                                                                                                                              |                                         | •               | ·                | ·               |                 | bit 8   |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                        | R/W-0                                   | R/W-0           | R/W-0            | U-0             | R/W-0           | R/W-0   |  |  |  |  |

| IC8IF           | IC7IF                                                                                                                        | AD2IF                                   | INT1IF          | CNIF             | _               | MI2C1IF         | SI2C1IF |  |  |  |  |

| bit 7           | 10711                                                                                                                        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                 | U.I.I.           |                 |                 | bit 0   |  |  |  |  |

| Legend:         |                                                                                                                              |                                         |                 |                  |                 |                 |         |  |  |  |  |

| R = Readable    | bit                                                                                                                          | W = Writable                            | bit             | U = Unimplei     | mented bit, rea | d as '0'        |         |  |  |  |  |

| -n = Value at F | POR                                                                                                                          | '1' = Bit is set                        |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |  |  |  |  |

|                 |                                                                                                                              |                                         |                 |                  |                 |                 |         |  |  |  |  |

| bit 15          | U2TXIF: UAF                                                                                                                  | RT2 Transmitte                          | r Interrupt Fla | g Status bit     |                 |                 |         |  |  |  |  |

|                 | •                                                                                                                            | request has oc                          |                 |                  |                 |                 |         |  |  |  |  |

| <b>h</b> :+ 4.4 | -                                                                                                                            | request has no                          |                 |                  |                 |                 |         |  |  |  |  |

| bit 14          |                                                                                                                              | RT2 Receiver Ir                         |                 | Status Dit       |                 |                 |         |  |  |  |  |